Review Article

# Simulation & performance analysis of various R2R D/A converter using various topologies

#### **Abstract**

This paper presents the study of R2R D/A converter using various topologies like CMOS, Transmission Gates (TG) and OP-AMP. For the sake of simplicity 4 bit input is taken. The R2R D/A converter consist of only two values of resistor R & 2R. By using the repetitive arrangement of precision resistor network in a ladder. The simulation of the R2R D/A converter has been done on the TANNER-EDA T-SPICE and the circuit verification has been done on S-EDIT on TANNER-EDA software package. Simulation results are included to demonstrate the results. The outcomes of simulation are fairly in agreement with the theoretical estimation.

**Keywords:** R2R D/A, CMOS, Op-amp, transmission gates

Volume 4 Issue 2 - 2018

## Pawan Whig, S N Ahmad, Anupam Priyam<sup>3</sup>

<sup>1</sup>Vivekananda Institute of Professional Studies, GGSIPU, India <sup>2</sup>Department of electronics and communication engineering, Jamia millia Islamia Central University, India <sup>3</sup>Project Fellow CSIR- National Physical Lab

Correspondence: Pawan Whig, Department of electronics and communication engineering, Jamia millia Islamia Central University, India, Email pawanwhig@gmail.com

Received: January 30, 2018 | Published: April 04, 2018

#### Introduction

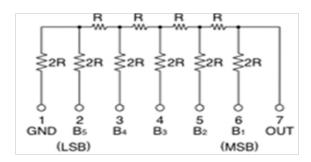

Most of the modern wireless communication systems require a wireless frequency (RF) subsystem.1 The design of RF system consists of various components ranging from connecting modules to power supply, antenna, baseband layer, and other interfaces, constitute a radio system.<sup>2-4</sup> The main front end radio transmitter module consists of digital signal processor which processes the input digital signal to analog output signal and visa versa. In other words, a discrete-amplitude; discrete-time digital input signal is converted into a continuous-amplitude, continuous-time analog counterpart. In most of the cases the input digital signal is a binary-coded representation of an analog signal using N bits. The leftmost bit of the input digital word is usually called the most-significant bit (MSB), and the rightmost bit is called the least-significant bit (LSB).5-7 Now with the advancements in VLSI technologies CMOS based current mode DACs are the very much for many applications. The main features of CMOS like their high speed, low power, and cost effectiveness enable it successful for the implementations in designing of circuits.<sup>8–10</sup> Nevertheless the digital to analog converter (DAC) can equally be used as a standalone chip for SoCs. There are several digital to analog architectures for DAC designs which includes resistor string, R2R ladder networks, charge scaling, current steering, and segmented current steering. 11-13 Common problem with DAC to avoid glitches because of the rapid change of more than one digital input bit at a sampling time causes noise problems since resistors are noise sources. Because of which DAC output dose not result in expected value.<sup>14-17</sup> In this research studies a comparative R2R DAC using various CMOS topologies has been presented. It is well known fact that the binary weighted resistor D/A converted requires a wide range of resistance value and matched switch for each bit position. 18-22 The R2R D/A converter with an R-2R ladder network which eliminates these complications at the expense of an additional resistor for each bit is shown in Figure 1. Bit MSB and LSB are driven from logic gates. The operation of this converter can be considering the weights of different bits one at a time. This can be followed by superposition to construct analog output corresponding to any digital input word.

Figure I R2R D/A converter diagram.

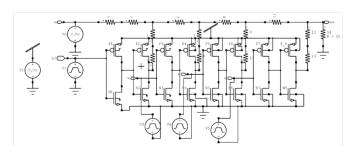

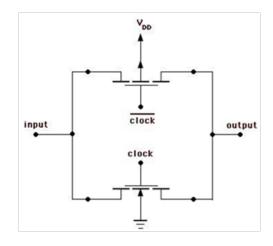

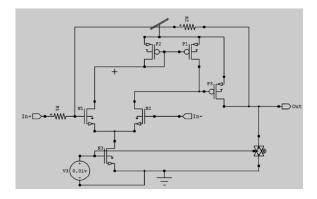

## **R2R D/A converter using CMOS**

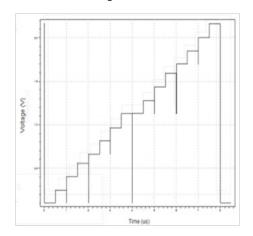

Figure 2 shows the R2R D2A converter using CMOS inverter. CMOS inverter is attached in series with next CMOS inverter for 1-bit and the R-2R series is attached with it, and then It gives output the same bit as input. The same process is repeated for all the bits. Figure 3 presents output in the analog form. The output Figure 3 of the R2 D/A converter is followed by the voltage as the voltage at node (n-1) is given by-  $V_{n-1} = V_R \left(\frac{R}{3R}\right) v$

$$V_{out} = -\frac{V_R}{2}$$

The weight of MSB is  $-\frac{V_R}{2}$

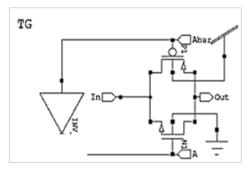

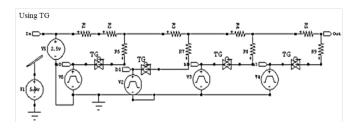

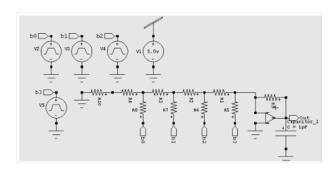

## R2R D/A converter using TG

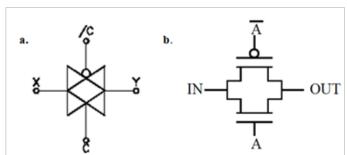

Transmission Gate (TG) is used in digital CMOS circuit design to pass or not pass a signal.  $^{23-25}$  In other words, it acts like switch. The gate is made up of the parallel connection of p- and n- channel MOSFET. When S is high then the transmission gate pass the signal on the input to the output. Transmission gate using CMOS and its circuit and symbols are shown in Figure 4–6. In the Figure 7 R2R D/A converter is using TG. In this  $b_0$ ,  $b_1$ ,  $b_2$  and  $b_3$  are the digital signal. The TG is a good switch and when the digital pulse is given to

129

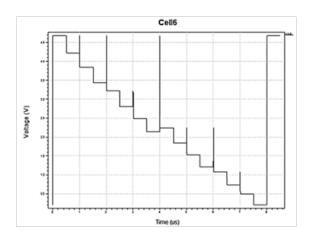

the entire bit it gives the output Figure 8 corresponding to the analog signal.

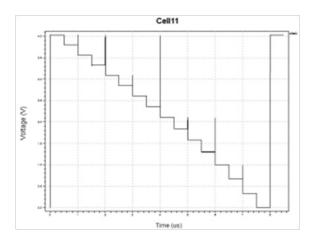

# R2R D/A converter using OP-AMP

The Figure 9 shows the internal circuit of op-amp which is used in the R-2R D/A converter using op-amp. When data is in binary form, the 0's and 1's where the logic zero may be a value up to 0.8 volts and the 1 may be a voltage from 3 to 5 volts. <sup>26–28</sup> The data can be converted to clean digital form using gates which are designed to be on or off depending on the value of the incoming signal. Data in clean binary digital form can be converted to an analog form by using a summing amplifier. For example, a simple 4-bit D/A converter can be made with an op-amp. Where the D's take the value 0 or 1. The digital inputs could be TTL voltages which close the switches on a logical 1 and leave it grounded for a logical 0. This is illustrated for 4 bits, but can

Figure 2 R2R D/A converter using CMOS.

Figure 3 Output of D2A converter using CMOS.

Figure 4 TG using CMOS.

be extended to any number with just the resistance values R and 2R. Input summing amplifier. More practical is the R-2R Network DAC. In the Figure 10, the negative input is at virtual ground, therefore the current through  $R_{TH} = 0$ .

Current through 2R connected to  $+5V = \frac{5V}{20} k\Omega = 0.25 mA$

The current will be the same as that in Rf.

$$V_{a} = -(20k\Omega)*(0.25mA) = -5V$$

Output voltage equation is given below.

$$V_{out} = R_f \left[ \frac{B_3}{2R} + \frac{B_2}{4R} + \frac{B_1}{8R} + \frac{B_0}{16R} \right]$$

The output is shown in Figure 11. with respective to the digital input and converting in analog output.

Figure 5 Circuit diagram of TG.

Figure 6 TG symbol a&b.

Figure 7 R2R D/A converter using TG.

Figure 8 Output of D/A converter using TG.

Figure 9 Internal structure of OP -AMP.

#### D/A using OP-AMP

Inference from Table 1: For the same technology i.e. CMOS technology developed for all the three design styles and the same power supply we arrive at the following comparative results:

Table I Comaprision analysis of various designs

| Design style Properties            | CMOS     | ТG          | OP-AMP   |

|------------------------------------|----------|-------------|----------|

| Technology used                    | CMOS     | CMOS        | CMOS     |

| Power supply(VDD, GND)             | 3.5V-0V  | 3.5V-0V     | 3.5V-0V  |

| Resistors                          | 9        | 9           | 10       |

| No. of components                  | 16 MOS   | 4TG (8 MOS) | 6 MOS    |

| Average power dissipiation (Watts) | 1.02E-02 | 3.80E-03    | 2.94E-02 |

| Maximum power dissipiation (Watts) | 9.67E-03 | 4.67E-03    | 4.13E-02 |

- a. Number of Components while implementing R2R D/A is least with OP-AMP as compared with other two design styles used.

- b. Power supply used in all the topologies remain fixed as shown in the table. 1.

Figure 10 D/A converter using OP-AMP.

Figure 11 Output of D/A converter using OP-AMP.

- c. The number of resistors required in case of CMOS and TG is 9 while with OP-AMP it is one more. This indicates the area of fabrication with the earlier two is least.

- d. The average power dissipation for the above three cases in Watts is listed as:

CMOS -1.02e-002

TG - 3.80e-003

OP-AMP - 2.94e-002

From this we come down to the conclusion that the average power dissipated is maximum in case of OP-AMP based R2R D/A circuit and the minimum in the case of TG. The Maximum power dissipation for the above three cases in Watts is listed as:

CMOS -9.67e-003

TG - 4.67e-003

OP-AMP - 4.13e-002

From this we come down to the conclusion that the Maximum power dissipated is maximum in case of OP-AMP followed by CMOS and TG as indicated above.

#### Conclusion

In this paper, R2R D/A circuit employing various topologies like CMOS, TG, and OP-AMP is proposed. As a result of the various

analysis made we arrive at following important results

OP-AMP > CMOS > TG - The average and maximum power dissipation (in Watts)

CMOS > TG > OP-AMP- (Number of component used)

The above results shows that although the implementation of R2R D/A circuit with OP-AMP dissipated more power but it requires less number of components as compared with other two topologies. The various advantages of implementing R2R D/A circuit is that it's very easy principle of working and construction another one its fast conversion rate as compared to other circuits. These advantages responsible for its use in audio and video techniques.

# **Acknowledgements**

I would be highly grateful towards My Institute Vivekananda Institute of Professional studies for giving me an opportunity to complete my research studies. Moreover I would like to express my gratitude towards Med Crave Group for publishing my research article in their esteemed journal.

#### Conflict of interest

The author declares there is no conflict of interest.

### References

- Myderrizi I, Zeki A. Current-steering digital-to-analogconverters: functional specifications, design basics, and behavioral modeling. *IEEE Antennas and Propagation Magazine*. 2010;52(4):197–208.

- Marche D, Savaria Y, Gagnon Y. Laser fine-tuneable deep-submicrometer CMOS 14-bit DAC. IEEE Translations on Circuit and Systems—I: regular papers. 2008;55(8):2157–2165.

- 3. Pawan Whig, Ahmad SN. Simulation of linear dynamic macro model of photo catalytic sensor in spice. *International journal of computation and mathematics in electrical and electronic engineering*. 2014;33(1/2).

- Seo D. A Heterogeneous 16-bit dac using replica compensation. IEEE Transactions on Circuit and Systems. 2008;55(6):1455–1463.

- Vaibhav Bhatia, Pawan Whig. A secured dual tune multi frequency based smart elevator control system. *International journal of research in* engineering and advanced technology. 2013.

- Pawan Whig, Ahmad SN. A Novel Pseudo NMOS Integrated ISFET device for water quality monitoring. Active and passive components. 2013;2013;6.

- Vaibhav Bhatia, Pawan Whig. Modeling and simulation of electrical load control system using RF technology. *International Journal of multidisplinary science and engineering*. 2013;4(9):44–47.

- 8. Takala J, Rostrom J, Vaaraniemi T, et al. A low-power MPEG audio layer 111 decoder IC with an integrated digital-to-analog converter. *IEEE Transactions on Consumer Electronics*. 2000;46(3).

- Greenley B, Veith R, Chang D, et al. A low-voltage 10-bit CMOS DAC in 0.01-mm2 die area. *IEEE Transactions on Circuit and Systems*. 2005;52(5):1–5.

- Pawan Whig, Ahmad SN. Development of economical asic for PCS for water quality monitoring. JCSC. 2014;23(6):1–13.

- 11. Jensen H, Galton I. A low-complexity dynamic element matching DAC

- for direct digital synthesis. *IEEE Transactions on Circuit and Systems*. 1998;45(1):13–27.

- 12. Pawan Whig, Ahmad SN. CMOS integrated VDBA-ISFET device for water quality monitoring. *International journal of intelligent engineering and systems*. 2014;7(1):1–7.

- Wei-Te Lin, Tai-Haur Kuo. A compact dynamic-performance improved current-steering DAC with random rotation-based binary weighted selection. *IEEE Journal Of Solid State Circuit*. 2012;47(2):444–453.

- Vaibhav Bhatia, Pawan Whig. Performance analysis of multi-functional bot system design using microcontroller. *International Journal of Intelligent Systems and Applications*. 2014;69–75.

- Pawan Whig, Ahmad SN. Development of low power dynamic threshold PCS system. *Journal of Electrical and Electronic Systems*. 2014;3(3):1–6.

- Risbo L, Hezar R, Kelleci B, et al. Digital approaches to ISI mitigationin high-resolution oversampled multi-level D/A converters. *IEEE Journal* Of Solid State Circuit. 2011;46(12):2892–2903.

- Pawan Whig, Ahmad SN. Novel FGMOS based PCS device for low power applications. *Photonic Sensor*. 2015;5(2):1–5.

- Pawan Whig, Ahmad SN. Impact of parameters on characteristic of Novel PCS. Canadian journal of Basic and applied Science. 2015;3(2):45–52.

- Ruchin, Chandan Mahto, Pawan Whig. Design and simulation of dynamic UART using scan path technique (USPT). *International Journal of Electrical, Electronics & Computer Science Engineering*. 2015;1:6–11.

- 20. Aastha Sharma, Abhishek Kumar, Pawan Whig. On the performance of CDTA based novel analog inverse low pass filter using 0.35μm CMOS parameter. *International Journal of Science, Technology & Management*. 2015;4(1):594–601.

- Pawan Whig, Ahmad SN. Simulation and performance analysis of low power quasi floating gate PCS Model. *International Journal of Intelligent Engineering and Systems*. 2016;9(2):8–13.

- Huynh J, Ngo B, Pham M, et al. Design of a 10 Bit TSMC 0.25μm CMOS digital to analog converter. IEEE; 2005:1–6.

- 23. Khafaji M, Gustat H, Sedighi B, et al. A 6-bit fully binary digital-to-analog converter in 0.25-µm sige bicmos for optical communications. *IEEE Transactions on Microwave Theory and techniques*. 2011;59(9):2254–2264

- pawan whig, ahmad sn. ultraviolet photo catalytic oxidation (UVPCO) sensor for air and surface sanitizers using cs amplifier. Global Journal of researches in engineering. 2016;16(6):1–13.

- Ajay Rupani, Deepa, Gajender, et al. A review of technology paradigm for IOT on FPGA. *International Journal of Innovative Research in Computer and Communication Engineering*. 2016;5(9):61–64.

- Pawan Whig, Ahmad SN. Simulation and performance analysis of multiple PCS sensor system. *Electronics*. 2016;20(2):85–89.

- Aliparast P, Bahar H, Koozehkanani Z, et al. A 12-Bit 1-Gsample/s Nyquist current-steering DAC in 0.35 μm CMOS for wireless transmitter. Circuits and Systems. 2011;2(2):74–84.

- Pawan Whig, Ahmad SN. Modelling and simulation of economical water quality monitoring device. *Journal of aquaculture & Marine Biology*. 2016;4(6):1–6.